在當今高速發展的信息時代,集成電路的性能、功耗和可靠性已成為衡量芯片優劣的核心指標。隨著工藝節點不斷微縮,工作頻率持續攀升,信號在芯片內部傳輸的時序問題變得愈發突出。傳統的靜態缺陷測試已無法全面覆蓋動態性能失效,因此,時延可測性設計應運而生,成為現代集成電路設計流程中不可或缺的關鍵環節。

一、 時延故障與測試挑戰

時延故障是指電路由于物理缺陷(如金屬線開路、橋接、晶體管參數漂移等)或工藝波動,導致信號傳播速度低于預期,無法在規定的時間窗口內達到穩定邏輯值,從而引發功能錯誤。這類故障是導致芯片在實際工作頻率下失效的主要原因。與靜態“固定型故障”不同,時延故障是動態的、與頻率相關的,其測試面臨巨大挑戰:

- 測試向量生成復雜:需要精確控制信號的時序關系,生成雙模式測試向量(Launch-On-Capture或Launch-On-Shift),以激活并捕獲路徑時延。

- 測試成本高昂:需要高速的測試設備(ATE)來施加高頻測試時鐘,且測試時間較長。

- 測試覆蓋不全:芯片中存在海量的潛在關鍵路徑,窮盡測試所有路徑時延在經濟和技術上均不可行。

二、 時延可測性設計的基本原理與方法

時延可測性設計通過在芯片設計階段植入特定的硬件結構,增強對內部時序特性的控制和觀測能力,從而高效、經濟地完成時延測試。其主要方法包括:

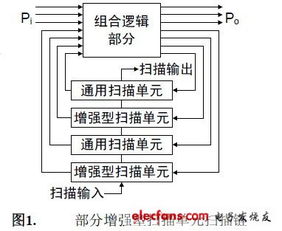

1. 掃描鏈增強設計

在標準掃描設計(DFT)基礎上進行擴展:

- 多時鐘域掃描:支持對異步時鐘域路徑的時延測試。

- 時鐘控制邏輯:集成精確的時鐘生成、選擇和門控單元,以產生測試所需的高速脈沖和時序序列。

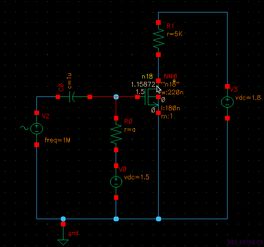

2. 內建自測試

- 時延BIST:在芯片內部集成測試模式生成器和響應分析器,通過片上環形振蕩器或延遲線產生高頻測試時鐘,實現對關鍵路徑的在線時延測量,大幅降低對外部ATE的依賴。

3. 路徑與時延故障模型

- 關鍵路徑選擇與隔離:通過靜態時序分析工具識別出對時序最敏感的關鍵路徑,并在設計中有選擇性地為其插入測試點(如觀測觸發器、控制多路器),確保這些路徑能被測試向量有效激活和捕獲。

- 過渡故障模型與路徑時延模型:前者關注單個門電路的上升/下降延遲,后者關注整個組合邏輯路徑的累積延遲,兩者結合能更全面地刻畫時延缺陷。

4. 片上時鐘與控制網絡

設計靈活、低偏斜的時鐘分布網絡,并集成可編程的時鐘延遲單元和脈沖發生器,為時延測試提供精確、可調的時序基準。

三、 設計流程與權衡考量

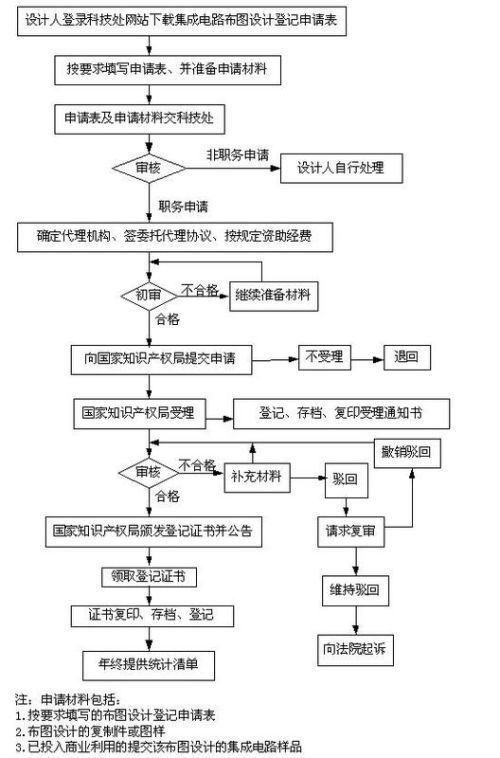

將時延可測性設計融入標準IC設計流程(從RTL到GDSII)至關重要:

- 前端設計階段:在RTL編碼時考慮測試結構,規劃時鐘與復位架構。

- 綜合與布局布線:在插入掃描鏈的考慮時延測試的布線約束,避免引入額外的關鍵路徑。

- 簽核與驗證:進行帶有時延測試模式的時序仿真和ATPG(自動測試向量生成)。

DFTD并非沒有代價,設計者必須謹慎權衡:

- 面積開銷:額外的邏輯(如多路器、觸發器、控制電路)會增加芯片面積。

- 性能影響:插入的測試點可能增加關鍵路徑的負載與延遲。

- 功耗增加:測試期間的高頻切換活動會導致動態功耗顯著上升。

- 設計復雜度:增加了驗證和物理實現的難度。

四、 未來發展趨勢

隨著工藝進入納米尺度及三維集成電路、異質集成等新技術的發展,時延可測性設計面臨新機遇與挑戰:

- 與自適應調頻調壓技術結合:測試結果可用于指導芯片的實時頻率-電壓調整,提升能效與可靠性。

- 機器學習輔助:利用AI算法預測關鍵路徑、優化測試向量集,提升測試效率與覆蓋率。

- 面向先進封裝:解決芯粒間互連的時延測試與監控問題。

- 在線監測與預測性維護:將時延監測電路作為永久性IP嵌入系統,實現芯片生命周期內的健康狀態追蹤與失效預警。

###

總而言之,時延可測性設計是連接芯片設計卓越性與制造可靠性的核心橋梁。它通過前瞻性的設計投入,將難以捉摸的動態時序缺陷轉化為可管理、可測試的工程問題,從而確保高性能集成電路在目標頻率下穩定工作。面對日益嚴峻的時序收斂挑戰和更高的質量要求,深入研究和應用先進的時延可測性設計技術,對于提升我國集成電路產業的整體競爭力具有重要的戰略意義。